Article

碳化矽 (SiC) 技術為電源、電動汽車和在家充電、大功率工業設備、太陽能應用和資料中心等多個行業顯著提高了功率傳輸和管理性能。

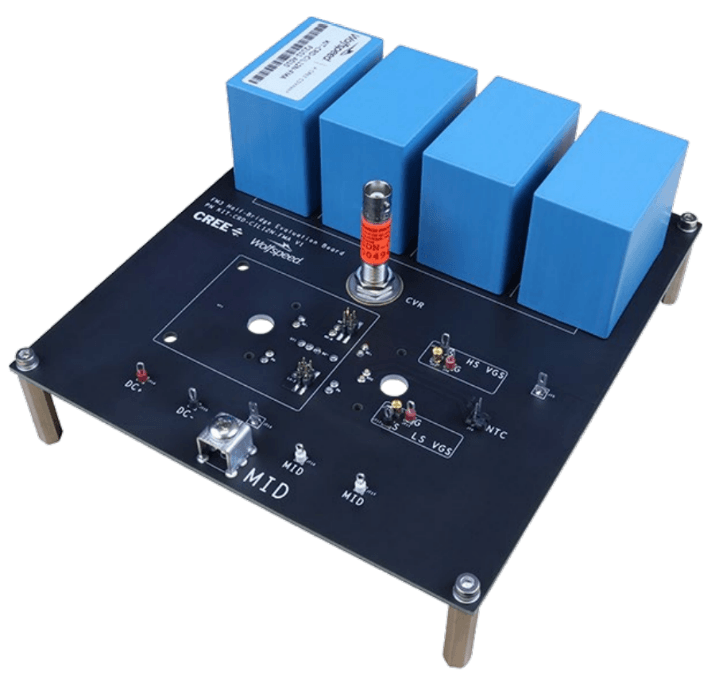

由於SiC更高的額定電壓、更低的系統運行溫度、具備更高的電流處理能力以及更出色的恢復特性,能為多種應用將效率及功率密度最大化,同時盡可能降低成本;然而,若想要充分利用 SiC 技術的優勢,將此類元件和性能進行表徵化就非常重要。 本文將詳細闡述 KIT-CRD-CIL12N-FMA 評估套件,特別是動態特性,以及為優化 SiC 功率模組開關性能所需的工具。

開展動態特性測試

為了測量MOSFET 動態性能的四個指標(包括開關損耗、時間、過沖、開關速度),必須使設備工作,然後使用鉗位元電感負載 (CIL) 測試系統進行高精度測量。

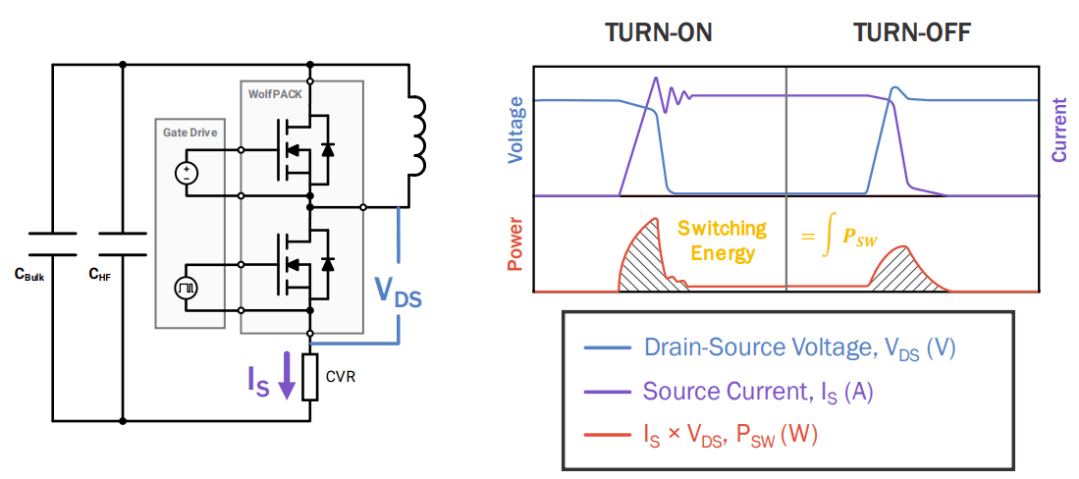

將 MOSFET 動態性能進行表徵化的第一步是使用雙脈衝測試 (DPT) 測量元件的電壓和電流。通過測量這兩種波形,可以提取並分析所有的資訊,包括損耗、時間、過沖以及開關速度/能量。圖 2 是半橋拓撲的典型設置方式,利用 WolfPACK 功率模組以及在測試時獲取的一些關鍵波形及測量資料。根據波形示意圖可以看出,當低邊開關開通時,將會呈現典型的開通波形,顯示峰值電流/過沖,以及 di/dt 和 dV/dt 以及 Vds。電壓和電流的乘積為暫態功率,結合來看,可以揭示從關斷狀態變化到開通狀態的開關能量。 在表徵過程中,一種不太常見的測試是二極體測試,其使用低邊開關的負載電感進行。這有助於在開關過程中將體二極體的性能進行表徵化,同時展現反向恢復性能。

系統PCB 以及柵極驅動器佈局的最佳實踐

另一個需要測量的重要方面則是加入柵極電阻後 MOSFET 性能的變化,其會改變電壓和電流(dv/dt 以及 di/dt)的變換速率,並增加開關損耗。對於多個 MOSFET 並聯的情況,建議每個 MOSFET 柵極配置1 Ω 到 10 Ω的柵極電阻(Rg),這有助於減少開關過程中的振盪,並避免 MOSFET 超出其最大額定電壓。

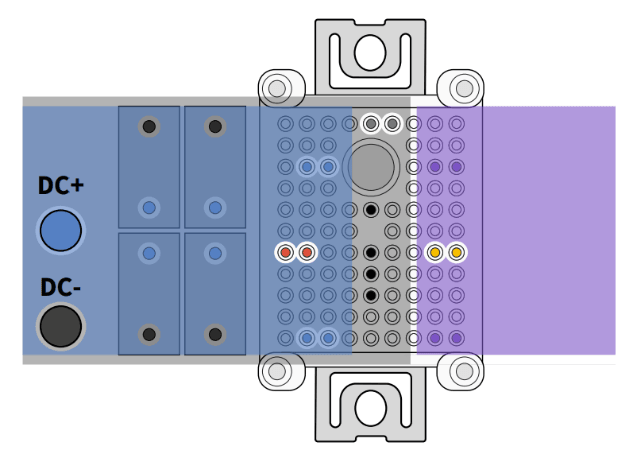

SiC 元件的實際佈局對過沖有顯著影響,這是由於寄生電感結合di/dt 會產生感應電壓(會疊加在母線電壓上)。由於 SiC 能夠實現更迅速的開關速率,其過衝要比矽 (Si) 高得多。所以,務必要遵循最佳佈局實踐,盡可能降低任何額外的電感。例如,直流匯流排應包含層壓銅平面,而每個模組和電容器之間的電感應相等。同時還應具有較大的表面積,幫助散熱,以及具備較厚的走線,盡可能減少自身電感。同時也應使平面重疊,以加強磁通相抵效果,如圖 3 所示。

在高壓線與匯流排連接的 PCB 上的額外層有利於提高去耦和磁通相抵效果,而直流母線電容和壓接引腳之間具備相等的電感/跡線長度同樣也很重要。WolfPACK 模組的輸出部分具備較寬的平面,可提供最大的電流載流量,這也是十分重要的。此外,不得將模組的輸入和輸出部分重疊,這會增加電容並使損耗變大。

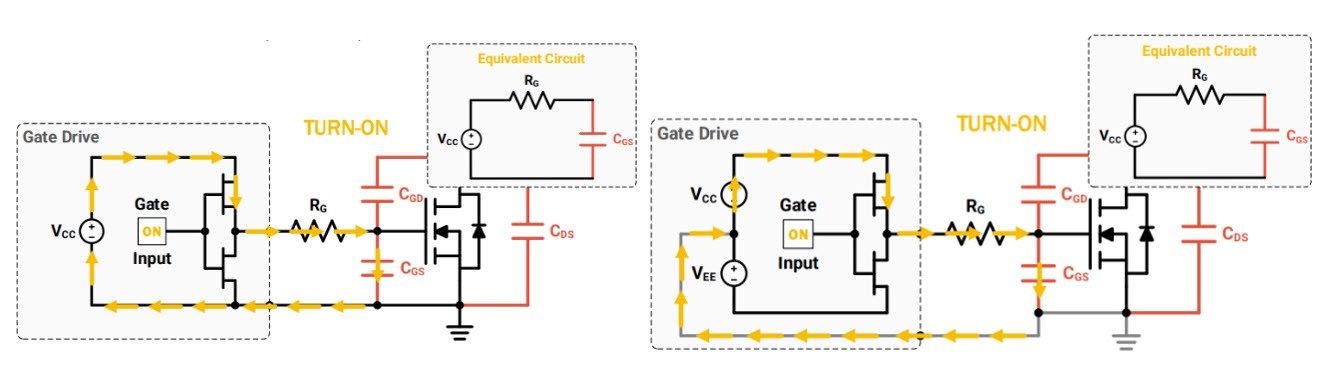

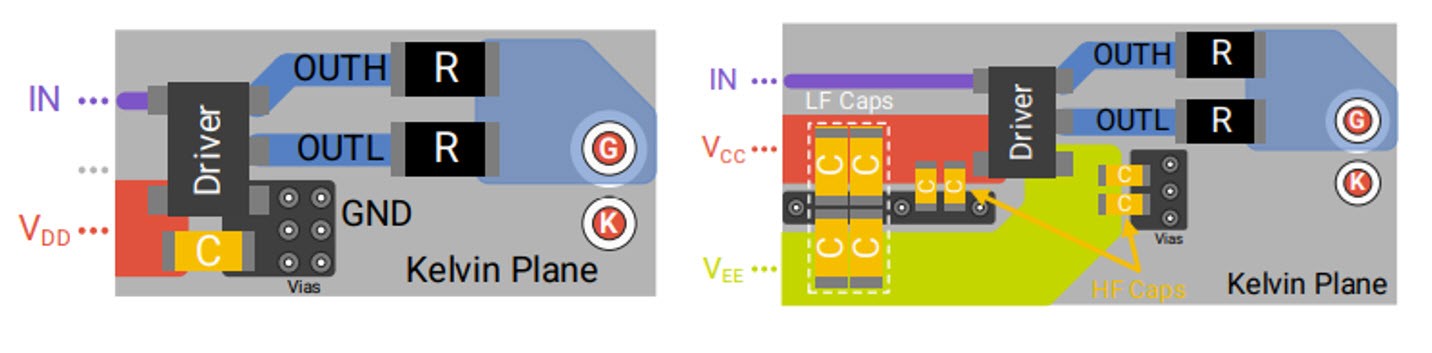

柵極驅動器主要有兩種配置方式。第一種是單極性,在“關斷”狀態下,功率 MOSFET 在不存在負偏壓的情況下保持關斷。第二種是雙極性,其中存在兩個電源,一個電源具有負電壓,在“關斷”狀態下保持設備關閉,並能提高整體可靠性。圖 4 示出了單極和雙極柵極驅動器在“開”狀態下的對比圖。

對於單極性配置,��建議為開爾文源極平面(MOSFET 的信號源極)配置成較大、較厚並位於所有元件的正下方,且包含多個連接至驅動器IC 旁路電容和功率端子的通孔(最大化電流載流量)。同時,為每一 MOSFET 設置不同的柵極電阻能夠帶來可調整性和不同的開/關速度等優勢。對於雙極驅動器來說,可能需要額外的一套電容器來提供額外的負電源。將高頻回路最小化是獲得最小電感、最大峰值電流、最低開關損耗以及最佳性能的關鍵。圖 5 示出了單極性和雙極性配置的最佳佈局。

如何測量寄生電感並將其表徵化

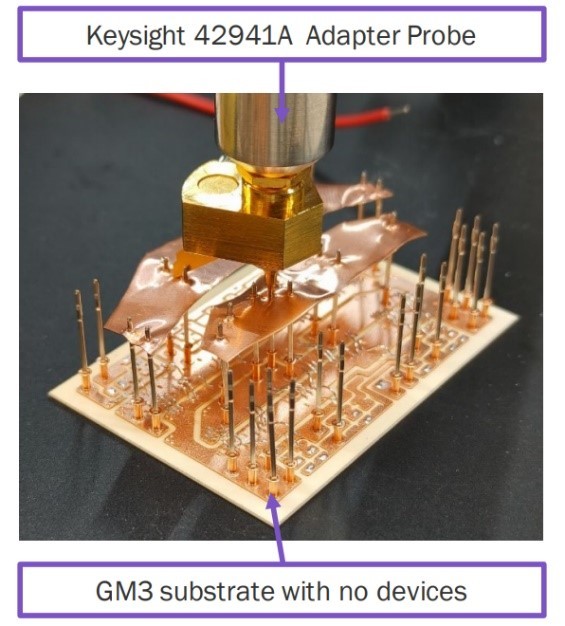

由於電感極低(通常低於 10 nH),因此測量 SiC MOSFET 模組的寄生電感可能非常困難。Keysight E4990A 阻抗分析儀是一款出色的工具,能夠測量一系列頻率(10 kHz 到 120 MHz)下的電感。為了與模組設備連接,需要 Keysight 特定探針中的一支,或者定制化、牢固的 PCB 設備(不含焊線/線纜/夾具),以確保最高水準的準確度。

將 Wolfspeed的 62 毫米 WolfPACK 模組以及三款使用相同設置的競品進行了寄生電感比較,發現 Wolfspeed CAB530M12BM3 功率模組的寄生電感(為 11.2 nH)顯著低於競爭對手(在 15.8–19.2 nH 之間)。GM3 WolfPACK 200-A 模組的寄生電感有些難以測量,但當移除所有設備 (MOSFET),留下焊線和引腳(見圖 6)時,便可以準確計算整體的雜散電感。GM3 在 10 MHz 運行條件下的原始測量值(含 MOSFET)為 15.8 nH,而補償電感(僅基板)在 10 MHz 運行條件下的測量值為 8.7 nH。用原始測量值減去補償測量值會得出功率模組的整體雜散電感,為 7.1 nH。這表明,對設備和探針進行補償非常重要,因為在使用阻抗分析儀時,它們會顯著增加電感數值。

在優化 SiC 系統時,必須考慮整體系統電感,不能僅考慮功率模組或電容。XM3 便是一個良好的示例。其具有 7 nH 的低電感,同時也能為母線與匯流排連接設計實現更低的電感 (6 nH)。那麼整體雜散電感為 13 nH,對系統整體來說頗有益處,能夠顯著減少開關過程中的過沖。

測量器件電流和電壓

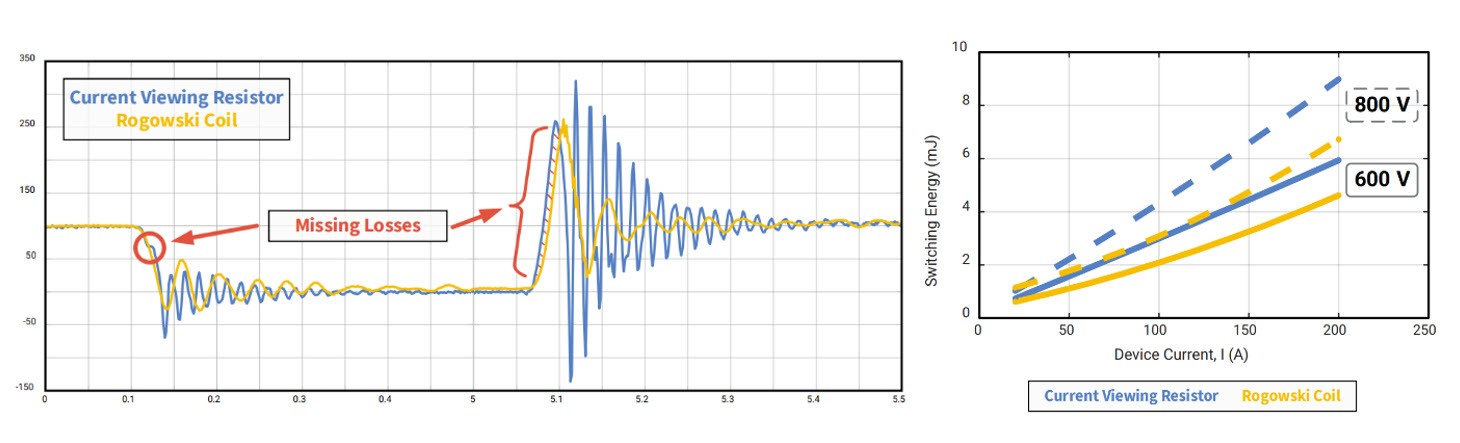

要想測量器件電流並得到準確的結果,這很大程度上取決於探針的品質。當處於較高頻率時,某些探針性能更為出色,與品質欠佳的探針相比,其捕捉的損耗和能測量的不穩定特性更準確。例如,在比較 T&M Research SSDN-005 探針和 Rogowski 線圈時 (PEM CWTUM/3/B),可以觀察到電阻器探針在 30 MHz 開關頻率(圖 7)以上探測到的振鈴更為明顯。圖片顯示 Rogowski 線圈感應到的開關能量有誤(低了 20%)。在為 MOSFET 的開關性能進行表徵化,並瞭解哪個頻率範圍會引入比預期更多的能量損耗時,這非常重要。

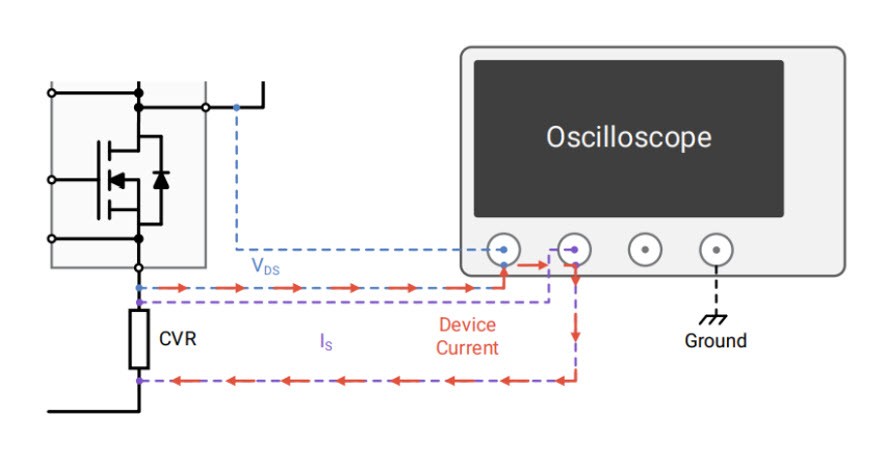

如圖 8 所示,在測量 VDS 時,接地非常重要。可以使用兩種探針進行測量:單端和差分。當使用單端探針時,要參考您的系統,避免存在多個接地點。如果直接測量 VDS,而不考慮 CVR,會導致結果異常,這是因為示波器有多個參考點。如果 復位CVR ,其參考點與 VDS 測量的參考點一致(提供反相信號,可以通過示波器調整),那麼結果便會得到改進。 差分探針是另一種出色的選項。進行低邊測量時,其表現良好,進行高邊測量時,其準確度欠佳,共模抑制比較高。Tektronix TPP0850 是良好的單端探針,而 Tektronix THDP0200 是一款出色的差分探針,額定 200 MHz,1,500 V。

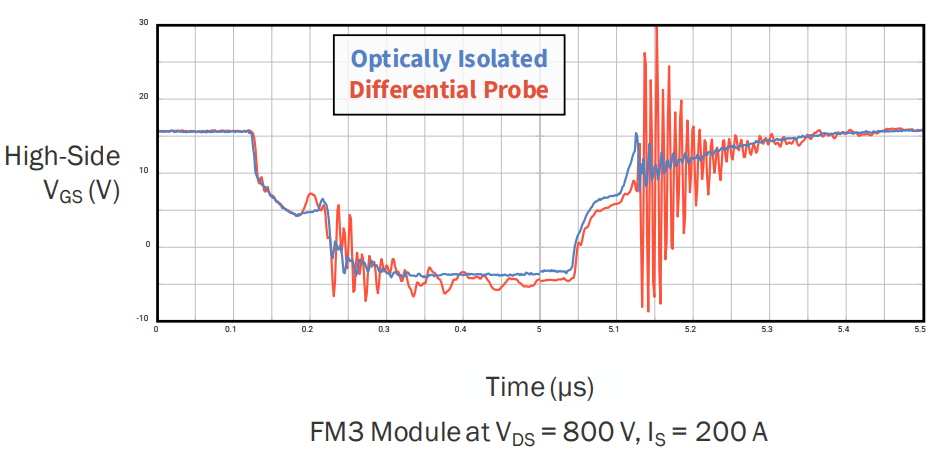

對於柵極源極電壓 (VGS),在比較光隔離探針和標準差分探針後,差分探針能探測到的振鈴更多(見圖 9)。當設計人員認為測量到的振鈴確實存在於系統之中,這能夠警告設計人員,這實際上僅是差分探針的一種測量固有數值。錯誤資訊是由於差分探針的低共模瞬變抗擾度 (CMTI) 與較高的 dV/dt 相遇而造成的。推薦 Tektronix IsoVu TIVH05 作為光隔離探針的理想之選。

後期處理和分析

在對多種元器件和配置進行測量之後,在分析和比較結果時,還需要考慮很多因素。建議對不同配置的開關動態特性進行定性評估,以找到適合於該應用的最佳配置。從測試方面來看,可能會多次重複這種流程,但當重疊波形時,便能夠得出最佳配置。

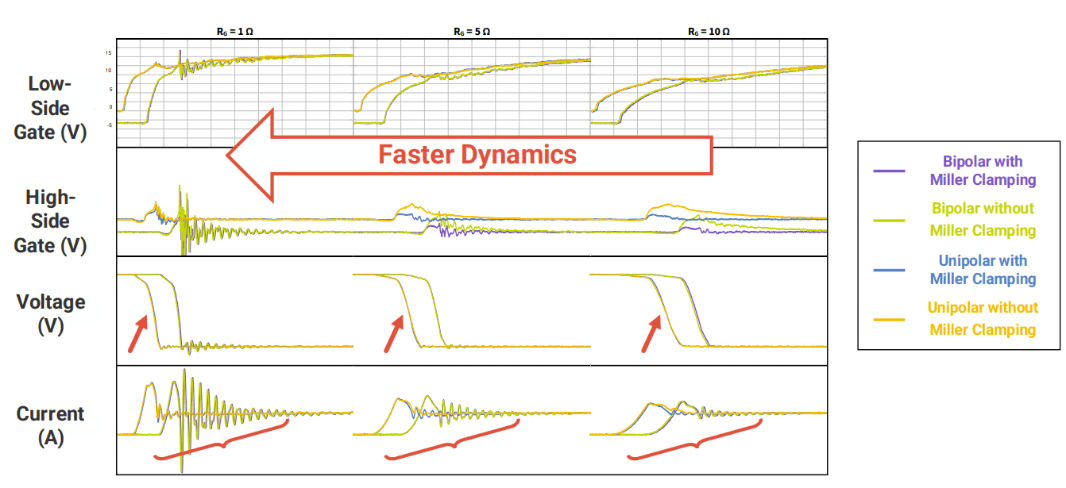

在專門研究柵極驅動拓撲時,圖 10 示出了MOSFET開通過程中從 1-Ω 到 10-Ω 的外部柵極電阻、低/高邊柵極電壓、電流以及雙極性/單極性和米勒/非米勒設計的多個測試示例。從圖表中我們可以看出,針對於該示例,較低的柵極電阻能夠帶來更快的開關頻率,但其較為激進,可能會造成性能不穩定(至少在沒有米勒鉗位元的情況下)。隨著柵極電阻增加,開關頻率變慢,米勒鉗位的優勢更為明顯。

該開通過程包含非常激進的開關表現,包含 150˚C 的虛擬結溫以及 100-A IDS,使得設計人員需要選擇較慢的開關速度和較高的柵極電阻來確保設計的穩定性。在關斷過程中,資料則明顯不同,在較低的柵極電阻下其表現不像開通過程中大幅變化如果可以接受採用1- Ω來進行關斷MOSFET,那麼可以通過相應地調整兩個柵極電阻,該設計的開關速度(最小化關斷延時)和可靠性(更低的過沖和振��鈴)將得以優化。使用相同的一套圖表還可以分析體二極體的反向恢復性能。

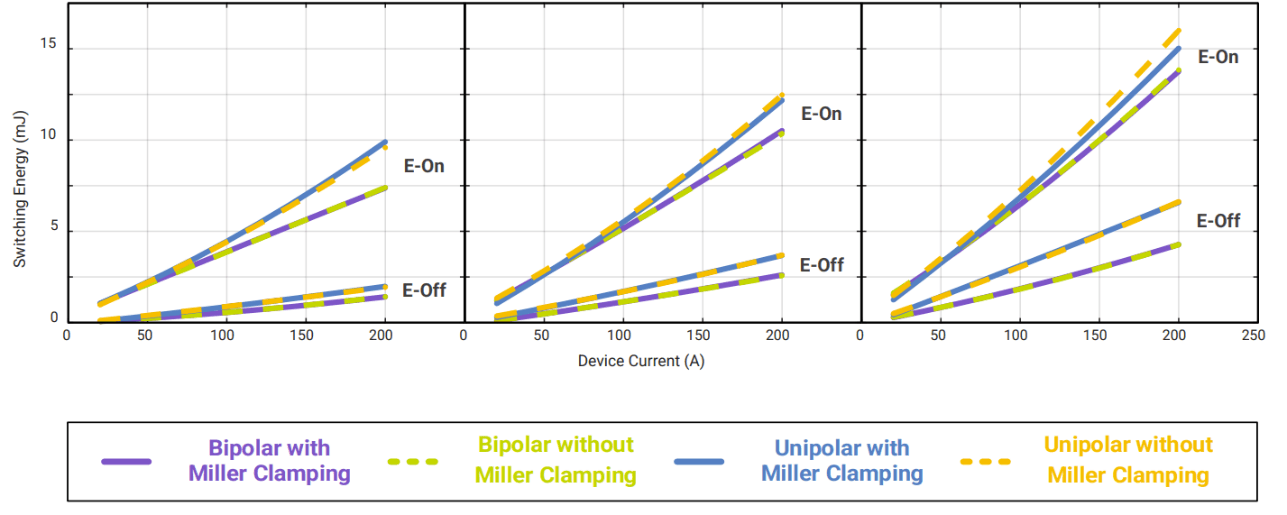

當進一步結合電壓和電流波形時,設計人員可以直觀地看到開關能量的表現,並比較所有情況下的開通/關斷能量(見圖 11)。在觀察這些圖表之後得出的一個關鍵結論是,採用帶米勒鉗位的雙極性柵極驅動器 (15 V/–4 V) 能夠帶來最佳的穩定性(不存在自開通、減少直通風險)和開關損耗。

在進行測試和後期處理時,務必查看 MOSFET 在整個結溫範圍內的表現。在室溫下 (25˚C),較低的柵極電阻可能能夠的滿足應用需求,同時最大化開關速度。然而,當溫度較高時,開關特性和反向恢復特性可能會發生劇烈的變化,導致損耗和不穩定性增加,使得 MOSFET 處於不安全的運行環境中。可採用加熱板(或類似方法)進行高溫測試,以模擬在正常運行條件下的實際溫度。

結論

考慮多種拓撲以及開關條件是非常重要的,還需要採用合適的設備才能準確地對設計進行建模。通過一系列測試方法得出四個關鍵指標(開關損耗、時間、過沖以及開關速度)後,便能夠選擇理想的配置方式,並進行設計優化,從而充分利用 SiC 的出色特性。