尋找適用的技術解決資料中心的電源挑戰

Article

數位化和雲端服務的快速部署推動了全球資料中心的成長。資料中心消耗全球將近1%的電力,預計此一數字還會成長。元宇宙、擴增實境和虛擬實境等業界趨勢將繼續消耗超出地球可持續生產的能源。雖然增加可再生能源的方向正確,但這還不夠,由於伺服器及其冷卻系統消耗著將近40%的資料中心運營成本,能源效率也是需要重點關注的領域。

資料中心電源的全球性標準也繼續朝著更高效率的方向發展。OCP開放計算專案3.0進一步最佳化硬體來降低能耗,80 Plus白金和鈦金認證要求,以及歐盟的節能化設計指令標準(ErP)Lot 9項目的法規也在不斷發展(表1)。Lot 9的下一次更新已經安排在2026年1月。

| Efficiency | Power Factor | 80 Plus | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Requirement | Output/Load | 10% | 20% | 50% | 100% | 10% | 20% | 50% | 100% | 230 V non-redundant | 230 V redundant |

| Lot 9 (March 2020) | Multi | — | 88% | 92% | 88% | — | — | 0.90 | — | Gold | Gold |

| Single | — | 90% | 94% | 91% | — | — | 0.95 | — | Platinum* | Platinum | |

| Lot 9 (Jan. 2023) | Multi | — | 90% | 94% | 91% | — | — | 0.95 | — | Platinum* | Platinum |

| Single | 90% | 94% | 96% | 91% | — | — | 0.95 | — | Titanium | Titanium | |

表 1:LOT 9 和 80 PLUS 的要求類似,80PLUS 鈦金應用要求 PFC 峰值效率超過 98.5%。

電源架構的演變

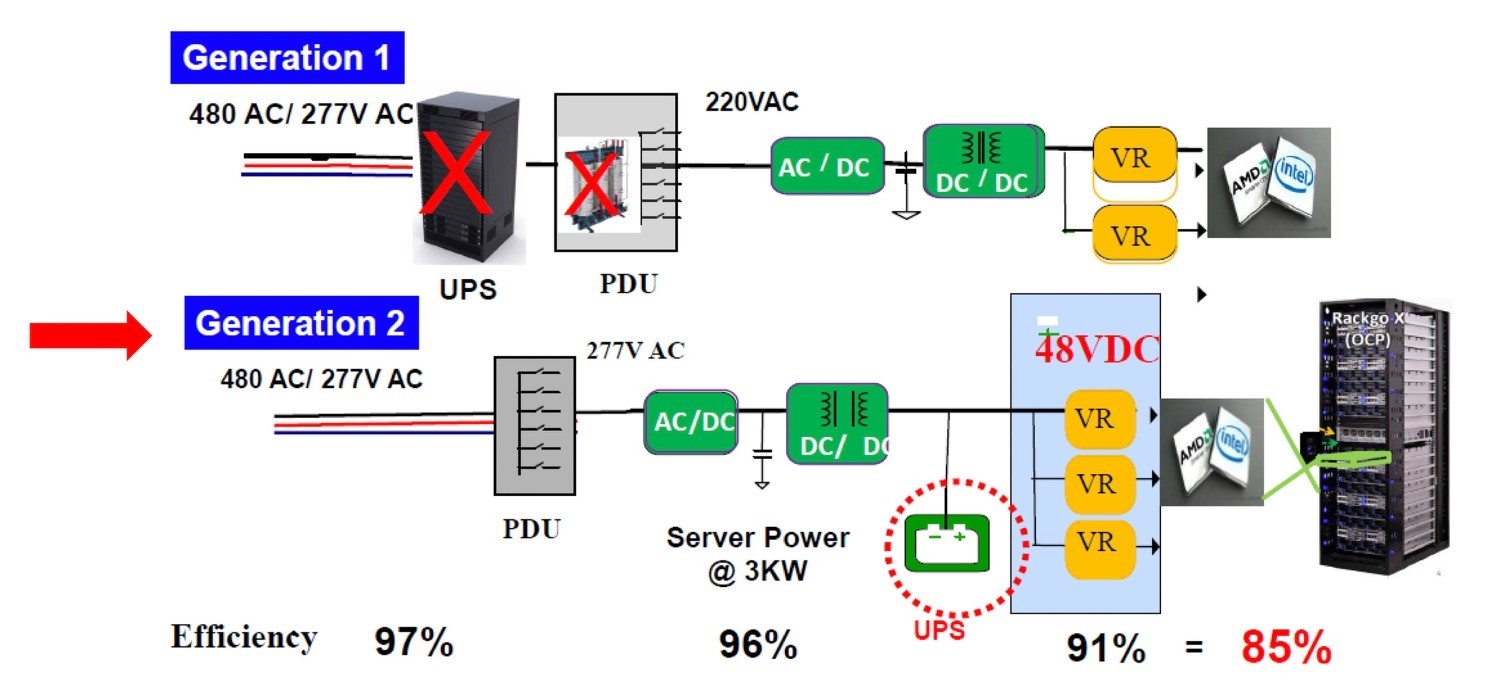

隨著處理器和伺服器功率增加,資料中心的每個機架也使用更多電源。隨著發展趨勢朝向更高功率密度,現時資料中心每個模組需要2-4 kW。[i]在第一代12 V系統中,這一功率意味著必須處理更高的電流。要向伺服器提供1 kW的功率,傳統的12 V架構需要提供83 A的電流。為了控制I2R損耗並解決安全問題,需要在此類系統的線束中使用更多的銅。

效率提升1%就可以使資料中心節省數千瓦的功率,而第二代電源架構採用48 V(圖 1),I2R損耗降低至十六分之一,同時仍低於UL-60950-1標準的60 V DC安全超低電壓(SELV)限制,超過這個限制就需要採取另外的絕緣、放置空間和測試。為了滿足新的能效要求,企業的資料中心電力方面因此開始採用48 V架構。

第2代機架系統通常採用個別的2-4 kW電源模組設計,每個機架使用以48 V DC電源充電的小型不斷電供應系統(UPS),取代了第1代大規模高壓UPS和配電單元(PDU)。AC-DC和DC-DC電源不僅為每塊伺服器主機板供電,還會為UPS電池充電。由於將第1代中的負載共用和冗餘移除,導致每個電源需在接近滿負載(100%)的情況下運行。

伺服器PSU面臨的挑戰

除了上述變化帶來的挑戰之外,值得注意的是,OCP 3.0、開放式機架V.2(ORV)和比特幣/挖礦電源供應器(PSU)需要超過2 kW,達到3-4 kW範圍。機架製造商持續要求小型和採用高度40 mm的低側高、高功率密度、有效和低成本的熱管理以及EMI設計,以實現高速開關和減少磁體的尺寸。而且,還要求使用安裝在印刷電路子板上的功率MOSFET,以實現全數位控制和設計的靈活性。

在考慮使用半導體元件技術解決這些挑戰時,必須注意能隙、臨界電擊穿、電子遷移率和熱導率方面的差異,所有這些因素都會影響系統的峰值工作溫度、電壓、效率和熱管理要求。

半導體解決方案

儘管矽(Si)是最常見的技術,但與氮化鎵(GaN)和碳化矽(SiC)等寬能隙材料相比,矽的能隙較小,從而限制了工作溫度,其較低的擊穿電場限制了矽在較低電壓下的使用,而較低的熱導率也限制了功率密度。

為滿足資料中心電源所需的高效率,功率元件的開關和傳導損耗都非常重要。當漏極和源極之間的導通電阻(RDS(ON))較低,並且隨溫度變化較小時,傳導損耗(即元件的I2R損耗)就會較低。

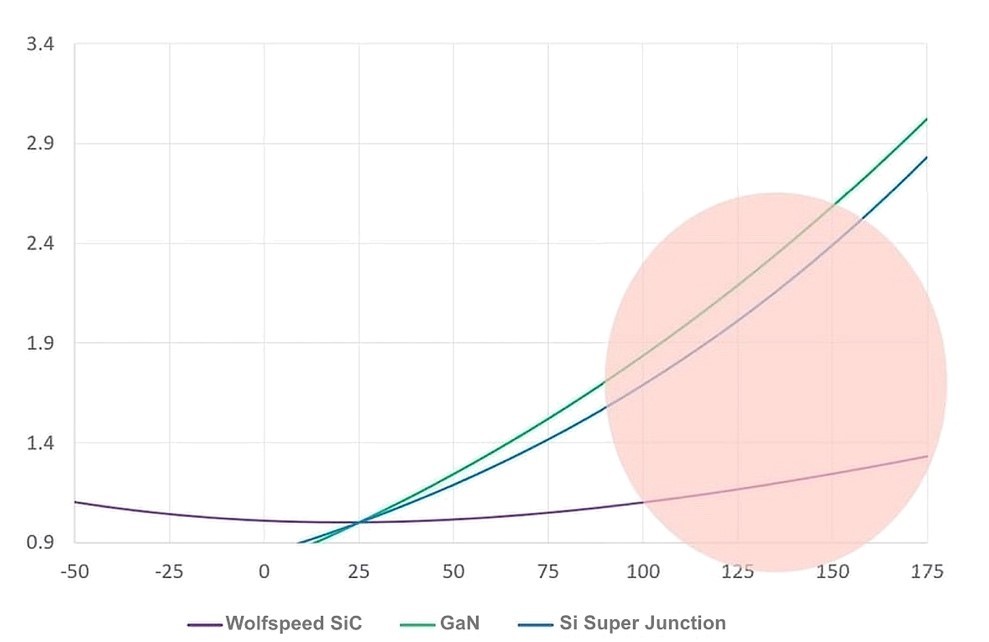

圖 2 顯示了正規化RDS(ON) 與溫度的關係曲線,許多設計人員都考慮使用這些技術來滿足第2代資料中心PSU要求,包括SiC、GaN和Si超級結(SJ)。值得注意的是,GaN和SJ元件在25 °C時都有較低的RDS(ON),對於資料中心電源而言,這個溫度數據不切實際。由於GaN和SJ元件的數據表通常規定RDS(ON) 在25 °C 時的值,這可能會誤導工程師,讓他們錯誤地假設這是正常設計時的系統工作溫度。

圖2中需要注意的另一個值得注意的特性是RDS(ON)隨溫度發生的變化。SiC的曲線幾乎保持平坦,但是其他技術的元件均顯示RDS(ON) 顯著增加,但這種變化對GaN來說尤其明顯。由於設計人員必須在120 °C至140 °C的實際結溫下使用RDS(ON),因此60 mΩ SiC元件的RDS(ON) 將產生80 mΩ時的熱量,而40 mΩ Si SJ或GaN元件的RDS(ON) 將產生遠遠超過80 mΩ時的熱量。

GaN 的低開關損耗 ¹ 低總損耗

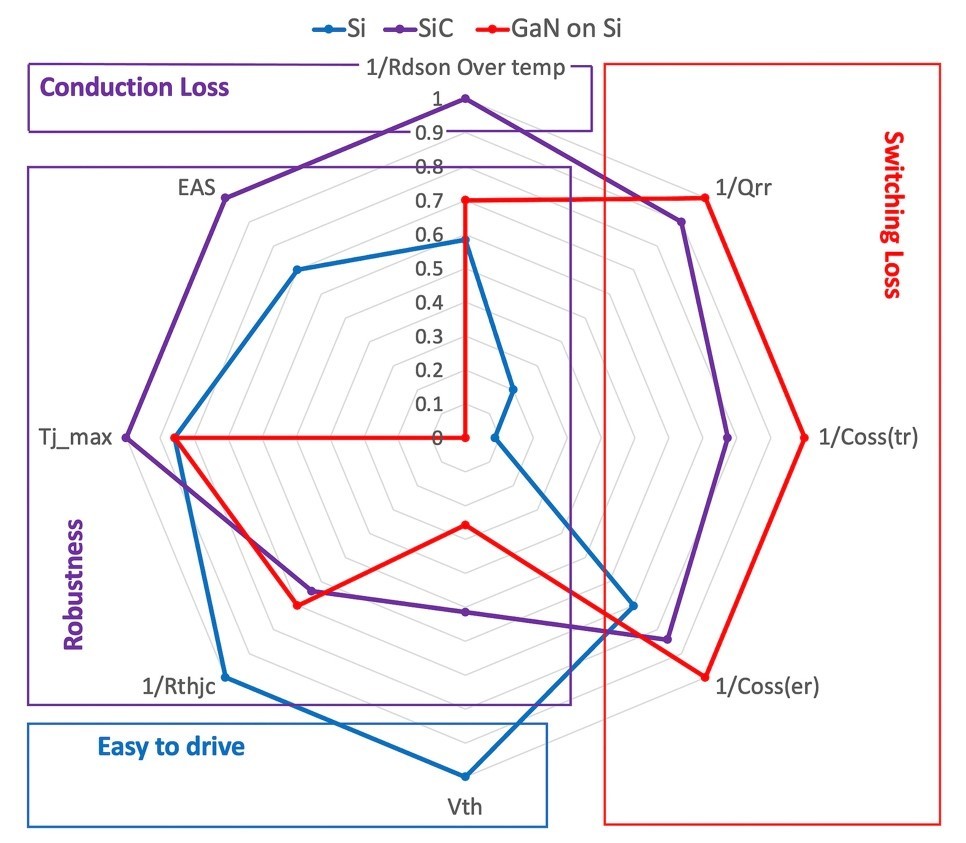

GaN的高電子遷移率特性使其在非常高的開關頻率下具有出色的效率,這點已經得到公認。在本文討論的技術中,GaN的開關損耗最低(圖 3)。

Wolfspeed在圖騰柱PFC模擬中將60 mΩ SiC元件與50 mΩ GaN元件進行了比較,發現儘管GaN在整個功率範圍內的開關損耗略低,但此一優勢都被隨功率增加及之後結溫升高而增加的導通損耗所抵消。這樣一來就需要將GaN元件製成較大尺寸,無論開關頻率如何,都可以補償更多的傳導損耗。

由於元件存在功率限制,GaN測試不得不在3 kW停止。該研究清楚地顯示,在更高功率下SiC的總損耗顯著降低,特別是使用寬能隙半導體的高功率應用最令人矚目,例如資料中心。圖4對三種半導體技術的各種元件級性能規格進行了比較。

乍看之下,我們注意到GaN的優勢是:在連續導通模式(CCM)同步整流器中,反向恢復電荷Qrr最低,開關損耗最低;在低死區時間、高頻率和高效率下,時間相關的輸出電容Coss(tr)最低;在硬開關拓撲中,能量相關的輸出電容Coss(er)最低,開關損耗最小。請注意,SiC在這些屬性上緊隨GaN之後,而Si則明顯落後。

矽的優勢包括結殼熱阻Rthjc最低,因此具有更好的熱性能,以及最高的閾值電壓Vth,可提供更好的抗雜訊能力,使Si元件更易於驅動。請注意,GaN的Vth極低。

最大結溫Tj_max和雪崩能量、單脈衝Eas顯示元件的穩定性。如圖所示,SiC最穩定,而GaN不具備Eas能力。

SiC在整個溫度範圍內的RDS(ON)變化最小,因此高溫時的傳導損耗較低。在這種情況下,GaN會顯著滯後,從而抵消低開關損耗帶來的所有優勢。

綜上所述,SiC的優勢有助於在更高的功率水準下,為企業資料中心和類似要求嚴苛的應用提供最高的效率和功率密度。

從封裝來看的觀點

由於Wolfspeed開發的SiC技術成功從Si轉換過來,因此許多常見的表面貼裝和通孔封裝也可用於SiC產品。然而,GaN面臨封裝標準化帶來的獨特挑戰。

例如,GaN通孔封裝並不常見,因為產品需要具有較低的寄生效應,並允許使用超高頻開關以最大程度利用材料的優勢。GaN通常採用大型QFN或客製化封裝。大型QFN存在電路板等級的可靠性問題,客製化封裝缺乏多源可用性,分包商的加工能力也不足。

GaN帶來的功率元件封裝挑戰不止於此。其他常見問題還包括:

- 凱爾文源極引腳(Kelvin source pin)在SiC中受到廣泛採用,可減小驅動回路雜散電感,實現更好的開關控制,但在串接式GaN中並不可行,因為其內部電容以及串接的低壓MOS等寄生參數無法應對。共源極無法消除,共源共閘GaN僅限於TO-247-3(三引腳)封裝,其中閘極振盪的脆弱性限制了開關速度。

- 市場上的一些客製化封裝非常薄,限制了散熱器的可用空間。

- 市場上的另一種客製化封裝具有頂部冷卻,這需要使用具有高導熱性的熱介面材料(Tim)實現元件散熱。

- 另一種用於GaN的無引線(TOLL)封裝將閘極和凱爾文源極引腳放置在不同於標準Si的方向上,這使得從後一種技術進行轉換變得很麻煩。

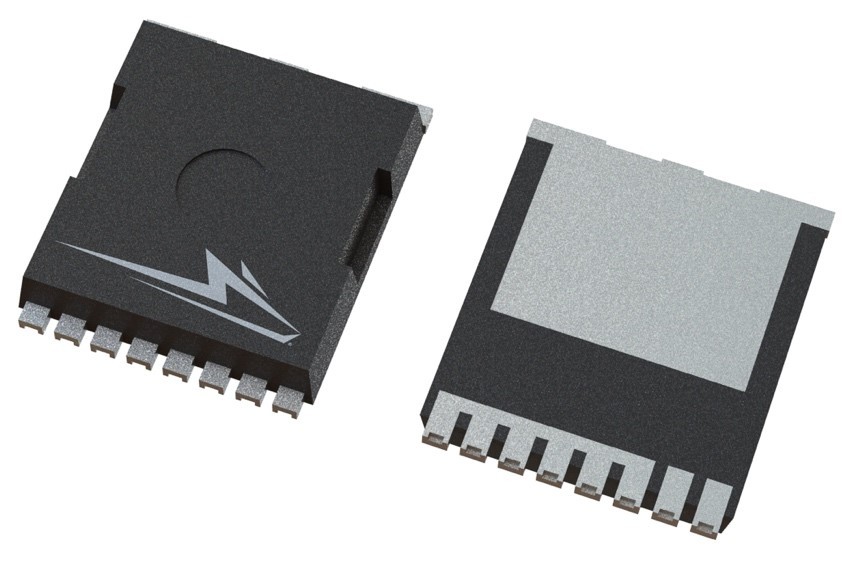

隨著市場轉向高功率密度設計和更嚴格的空間限制,無引線(TOLL)封裝具有高度低、尺寸小的優勢,其無引線封裝會降低引線電感,否則會成為高頻操作中的一個問題。這種封裝的漏極焊盤面積更大,解決了小封裝散熱性能問題。

對於資料中心和伺服器電源市場而言,TOLL 是一種相對較新的封裝方式。然而,Wolfspeed正開發這一方向的產品來支持該市場,例如用於資料中心和伺服器電源的新型TOLL封裝。

系統級比較

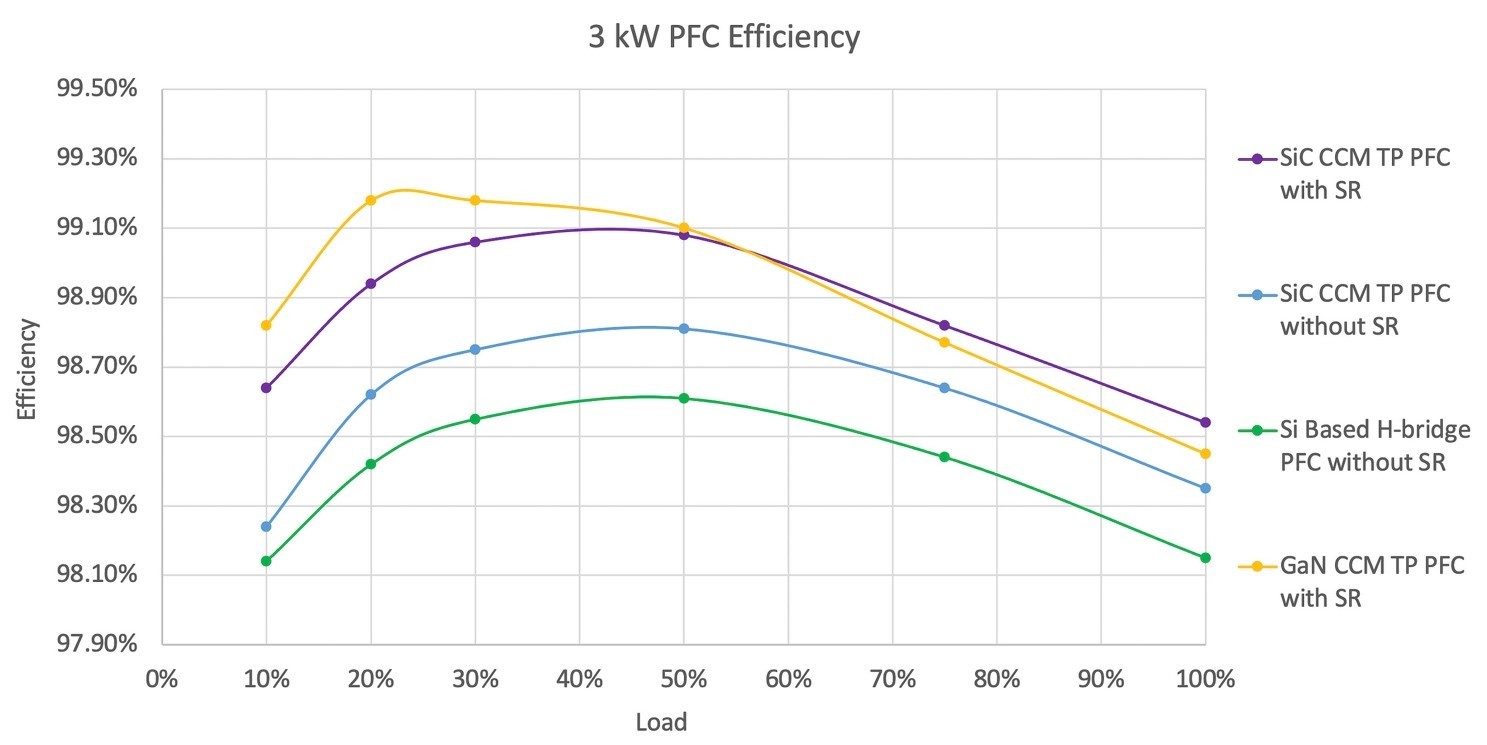

與基於Si的H橋相比,基於SiC的CCM圖騰柱PFC不僅具有更高的效率,而且在相同或更低的成本下具有更高的功率密度。不同技術之間的效率比較清楚地表明,雖然基於SiC和GaN的CCM圖騰柱PFC可以實現99%以上的效率,但 GaN僅在非常輕的負載下具有效率優勢。如前所述,GaN的RDS(ON) 隨溫度的變化要大得多(圖 2),這導致其效率曲線在較高功率或負載下急劇下降。因此,在資料中心等需要全天候或接近全天候滿負載運行的應用中,GaN無法滿足效率要求。另一方面,SiC在半負載時的效率與GaN相似,在滿負載時效率更高(圖 5)。

從更廣泛的角度來看,包括SiC和GaN基於CCM圖騰柱PFC的功率密度、元件數量和相對成本(表 2),我們注意到在高功率密度應用中,SiC不僅在效率方面優於GaN,而且在閘極驅動複雜性、控制和成本方面也優於GaN。

# PFC Choke | # Power Semiconductor | Power Density | Peak Efficiency | Cost | # Control | # Gate Drive | |

|---|---|---|---|---|---|---|---|

SiC CCM Totem Pole Semi-BL PFC | 1 | 4 | Highest | 98.8% | Medium | 2 | 2 |

SiC CCM Totem Pole bridgeless PFC | 1 | 4 | Highest | 99.1% | High | 3 | 3 |

GaN CCM Totem Pole Semi-BL PFC | 1 | 4 | Highest | 98.8% | High | 2 | 3 |

GaN CCM Totem Pole bridgeless PFC | 1 | 4 | Highest | 99.2% | Highest | 3 | 4 |

GaN CRM Totem Pole bridgeless PFC | 2 | 6 | Medium | 99.1% | Highest | 4 | 5 |

表 2:SIC 和 GAN 基無橋 PFC 的拓撲和元件分析。

在對不同公司的寬能隙元件設計的另一項比較中,Wolfspeed SiC顯示出明顯優勢(表3)。需要注意的一些要點是:

- 許多現有的參考設計要求實現不切實際的散熱管理,並限制了設計的靈活性。

- 由於RDS(ON) 的溫度係數較高,基於GaN FET的圖騰柱設計在滿負載時效率較低。

- 正如預期的那樣,SiC的低RDS(ON) 溫度係數使Wolfspeed的設計從半負載到滿負載呈現出近乎平坦的效率曲線。

- 雖然SiC和GaN可滿足2-4 kW範圍內的無橋PFC要求,但高傳導損耗使GaN散熱設計在4 kW以上面臨挑戰。

- 為滿足CE的EMI要求,參考設計的系統頻率限制在45-47 kHz和60-67 kHz範圍內,將諧波保持在150 kHz以下,這就抵銷了GaN的低開關損耗優勢。

Peak Efficiency | Full-Load Efficiency | HF Switch | LF Switch | Height (mm) | Power Density (W/in3) | Efficiency Standard | Physical Standard | Comments | |

|---|---|---|---|---|---|---|---|---|---|

Company A 2.6kW | 99.14% | 98.7% | GS66516B 32mΩ GaN | IXFH60N65X2 | 40 | 78 | 80+ Titanium/ ErP Lot9 | None | SMD GaN |

Company B 2.5kW | 99.2% | 98.5% | IGO60R070D1 70mΩ GaN | IPT65R033G7 | 45 | / | 80+ Titanium/ ErP Lot9 | None | eGaN, limited to 2.5kW by 70 mΩ |

Company B 3kW | 98.9% (50% load) | 98.5% | IMZA65R048M1H 65mΩ GaN | IPW60R017C7 (SJ MOS) | 40 | 32 | 80+ Titanium/ ErP Lot9 | OCPv3 | PFC SiC primary & Si secondary, LLC Si. No daughter card. |

Company C 4kW | 99% | 98.55% | GAN041-650WSA 41mΩ GaN | STY139N65M5 | 50 | / | 80+ Titanium/ ErP Lot9 | None | Cascode GaN |

Company D 3.6kW | 97.7% | 97.1% | SCTW35N65G2V 55mΩ GaN | TN3050H-12GY | 57 | / | 80+ Titanium/ ErP Lot9 | None | SiC, SCR, low efficiency |

Company E 4kW | 98.73% | 98.57% | LMG3410R050 50mΩ GaN | STY139N65M5 | 35 | 123 | 80+ Titanium/ ErP Lot9 | None | GaN, Interleaved, switching at 115 kHz (in CE bnad=nd)=) |

Company F 3.3kW | 99% | 98.55% | TP65H050WS 50mΩ GaN | STY139N65M5 | 50 | / | / | None | Cascode GaN |

Wolfspeed 2.2 kW | 98.79% | 98.68% | C3M0060065J/K 60mΩ GaN | FRED diode | 64 | 20 | 80+ Titanium/ ErP Lot9 | None | SiC, no SR |

Wolfspeed 3.6 kW | >99% (50% load) | >98.5% | C3M0045065L 45mΩ SiC TOLL | VS3CDU06H (diode) | 40 | 92 | 80+ Titanium/ ErP Lot9 | OCPv3 | SiC primary with SR option, daughter card concept |

表 3:市場上寬帶隙參考設計的競爭分析。

Wolfspeed的3.6 kW解決方案

Wolfspeed的全新3.6 kW圖騰柱PFC參考設計(表3,最後一行)旨在解決資料中心和伺服器電源挑戰,在半負載時效率超過99%,滿負載時效率超過98.5%,達到80 Plus鈦金和ErP Lot 9要求。

4 x MOSFETs | 2 x MOSFETs in HF leg + 2 x Diodes in LF leg | |

|---|---|---|

MOSFET cost % | 55.6% | 27.8% |

Diode cost % | 0.0% | 8.7% |

Gate drive cost % | 37.0% | 18.5% |

PCB, Heatsink | 3.7% | 3.7% |

Assembly cost | 3.7% | 3.7% |

Efficiency @ 50% | 99.1% | 98.6% |

Efficiency @ 100% | 98.9% | 98.5% |

Total cost 100% | 100.0% | 62.4% |

表 4:WOLFSPEED 的 3.6 KW 設計中四 MOSFET 和雙 MOSFET 選項的效率和成本比較。

該設計還提供了一定的靈活性,可以犧牲部分高效率以降低成本,但同時仍能滿足上述效率標準(表 4)。低成本選項用二極體取代設計中低頻(LF)管腳的兩個MOSFET,同時保留高頻(HF)管腳的兩個MOSFET。

雙子板設計概念使客戶能夠根據其系統設計優先順序靈活選擇合適的選項。在開發此類解決方案時,Wolfspeed利用其豐富經驗,開發出市場上經過最廣泛現場測試的SiC和基於SiC的GaN各類解決方案產品組合。Wolfspeed的半導體團隊最為瞭解這兩種技術的優勢和未來潛力,只有Wolfspeed才能開發出最適合任何特定應用的技術。

訪問 Wolfspeed 網站,了解更多關於 Wolfspeed 3.6kW 圖騰柱 PFC 參考設計的信息。

i WiWynn Corp. 等,48V:提升數據中心電力輸送系統性能(https://www.wiwynn.com/whitepapers/48v-an-improved-power-delivery-system-for-data-centers)