Modeling common topologies with Wolfspeed Silicon Carbide MOSFETs

Article

Now more than ever, engineers are choosing Silicon Carbide (SiC)-based products for their higher efficiency, power density, and better overall system cost effectiveness than Silicon (Si)-based components. Beyond the basic design principles common between SiC and Si, and the need to keep in mind SiC’s different characteristics, capabilities and advantages, engineers must model and simulate to ensure they will meet their design goals.

As with Si, SiC now has optimized tools and models available from various suppliers, and standard modeling mitigations can be applied. While there are differences between tools like LTSpice, PLECS, and Wolfspeed’s SpeedFit 2.0 Design Simulator™, tips from Wolfspeed’s Power experts will help achieve simulation accuracy with SiC.

Static simulation with LTSpice

Wolfspeed’s Spice models are optimized for 25ºC and 150ºC. The body diode operation is optimized for a drive voltage, VGS, of -4 V for Gen. 3 devices and -5 V for Gen. 2. Engineers can incorporate self-heating and transient thermal capability, and parasitic inductance. However, parasitic bipolar and associated effects, avalanche multiplication process, and variation of body diode turn-on voltage with gate-to-source are not modeled.

LTSpice static simulation results — the IV curve at various VGS values and the body diode curve — match up well with actual measurements. For capacitances — input capacitance, Ciss, output capacitance, Coss, and reverse transfer capacitance, Crss, too, the static simulation results are fairly close for the purpose. Engineers can therefore feel confident in the static parameters of the Spice modeling.

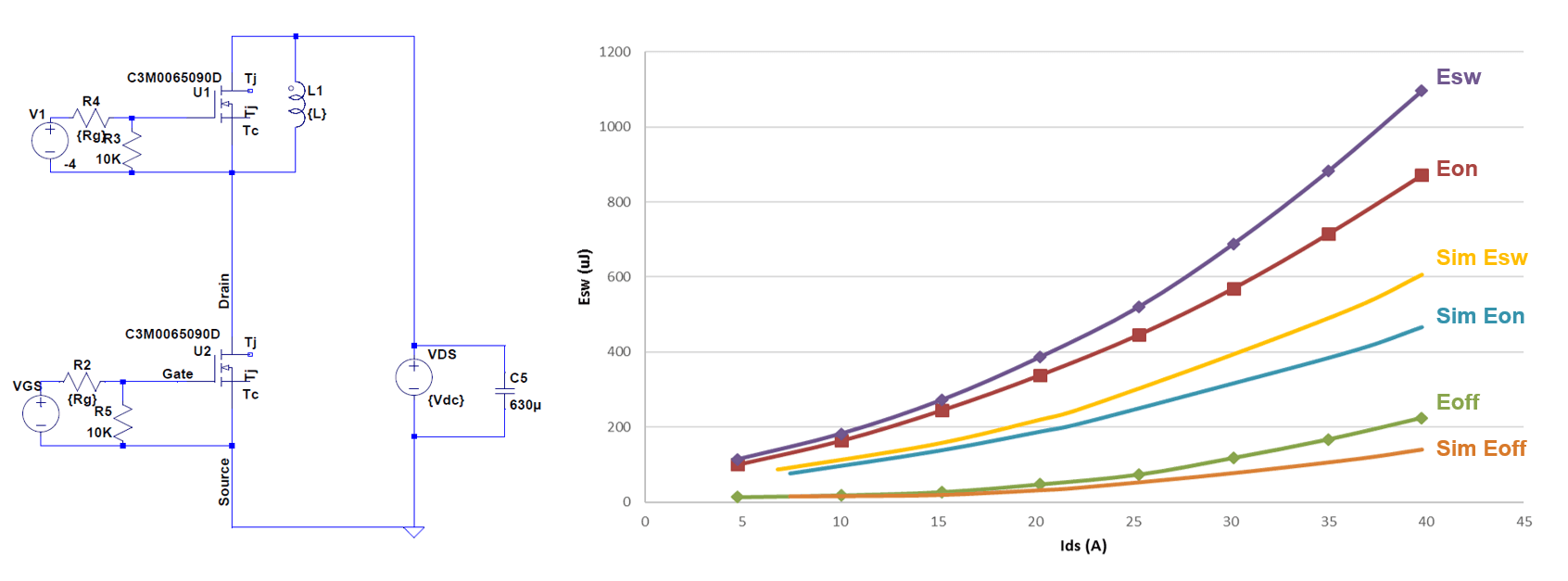

A double-pulse test

A typical characterization benchmark for understanding dynamic behavior is a half-bridge double-pulse test. When modeled without any considerations, such as parasitics, the simulation is significantly off the measured results (Figure 1). Since energy consumption impacts efficiency, such a big difference has a significant effect on thermal calculations.

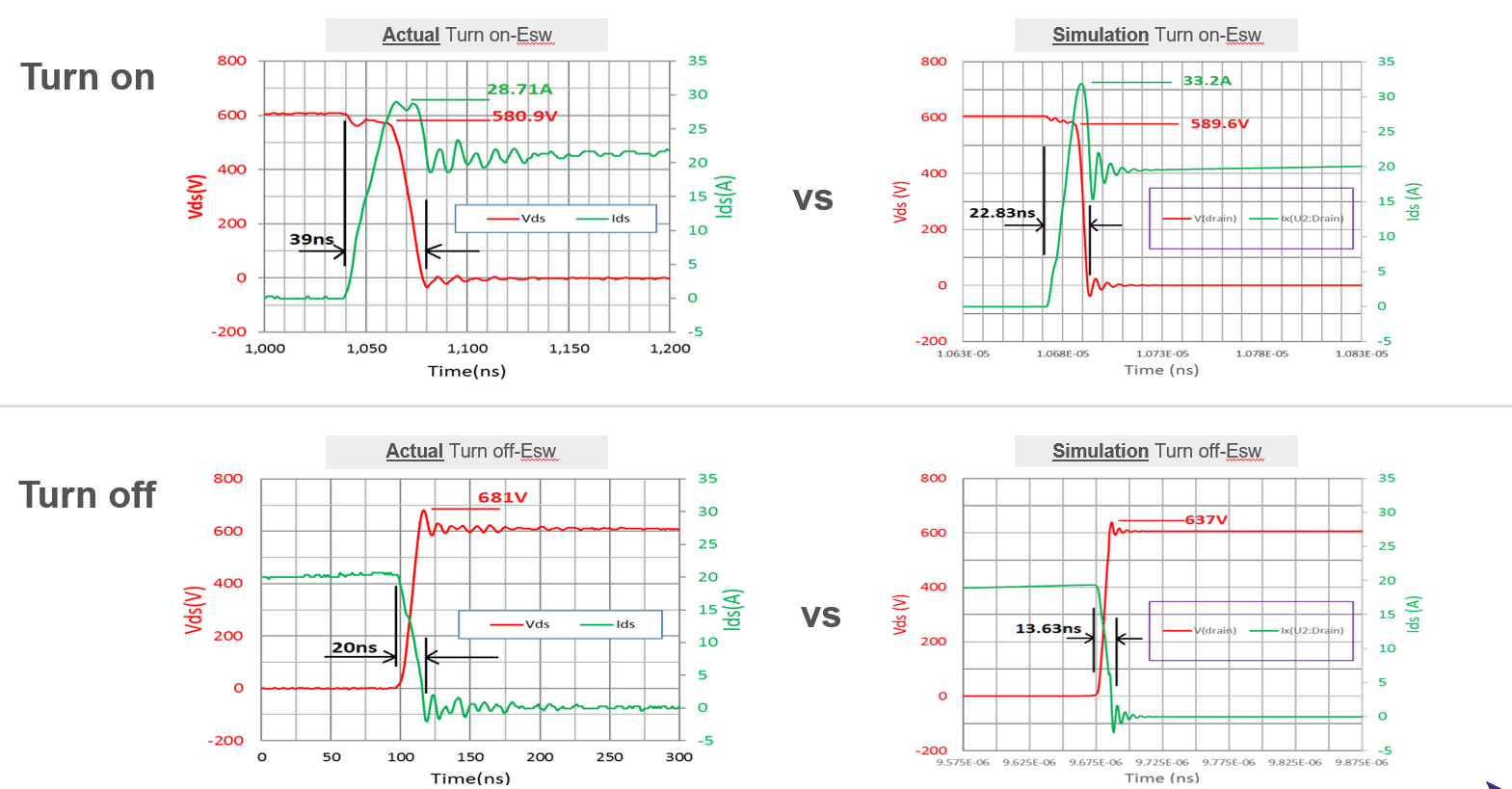

In the test case, a long pulse is followed by a 1 μs gap, which is followed by short pulse. Turn-on and turn-off are measured in the conventional way as one would with Si-based devices. Taking a closer look at the waveforms (Figure 2) highlights the difference between actual and ideal simulated results.

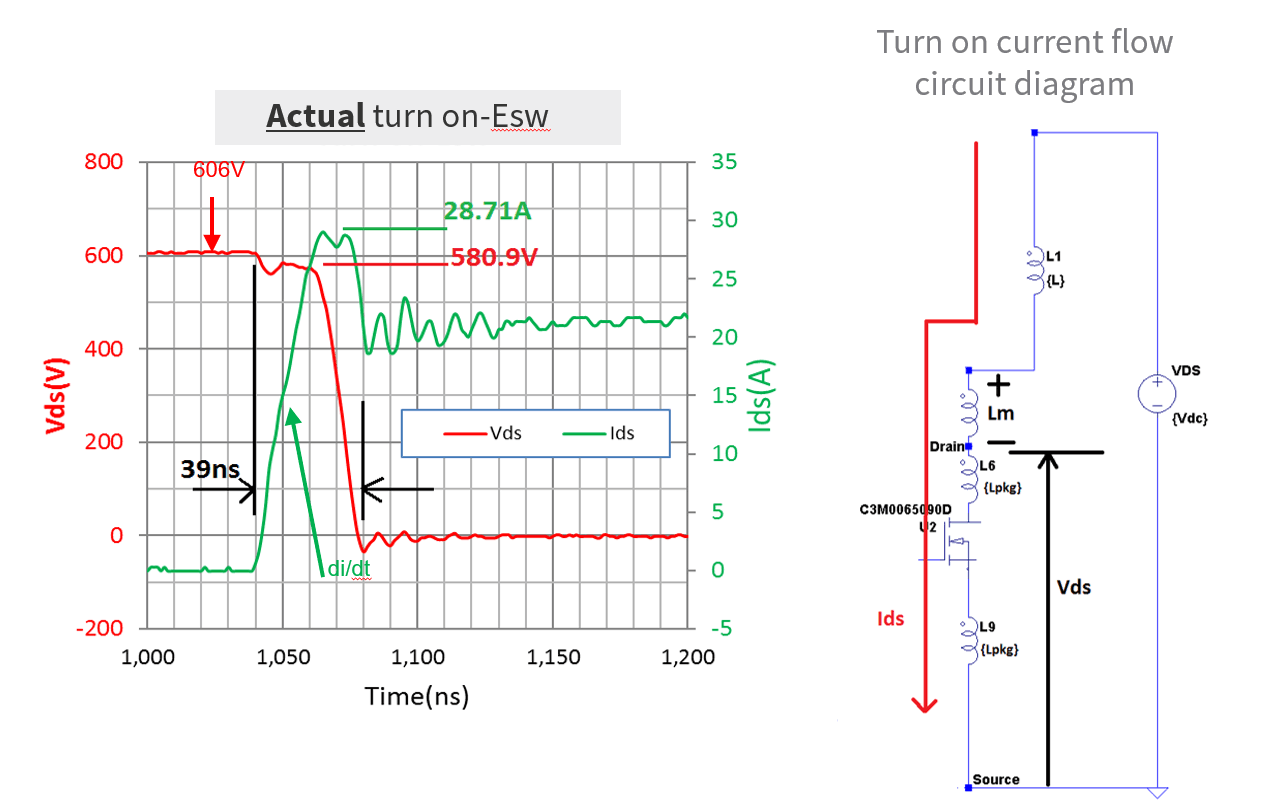

Both rise and fall times in the simulation are much faster than those measured because the actual results are affected by inductances — parasitic stray inductance, Lm, between the two devices, and package inductance, Lpkg, which is the source inductance of the package. There is also a difference between overshoot results for turn-on and turn-off. These differences contribute to the overall difference in switching losses.

To get an accurate model, the inductances must be extracted and manually imported into LTSpice. Thermal model in PLECS, on the other hand, does not include parasitic components.

Finding Lm

Lm is the inductance between the source of the high-side U1 device and the drain of the low-side U2 device. Although it can be directly measured, it can also be extracted thus (Figure 3):

Where:

This gives a value of 23.1674 nH for Lm

Whether it is a synchronous buck, synchronous boost, half-bridge or full-bridge, the design likely uses a configuration of high-side and low-side devices through a PCB. If good layout practices are followed, Lm is in the 20 nH-to-25 nH range. Engineers can regard that as a rule of thumb to use in simulations.

Extracting Lpkg

Designers might expect Lpkg to be the same across suppliers for standard packages like the TO-247. However, there are variations due to the differences in the thickness of lead frames, in source wire bonding, and in the length of the shoulder on the package. If available in a datasheet, it can easily be plugged into the model. If not, it can be extracted from a measured waveform and extrapolated to what might be a good estimate for the package at hand.

Where:

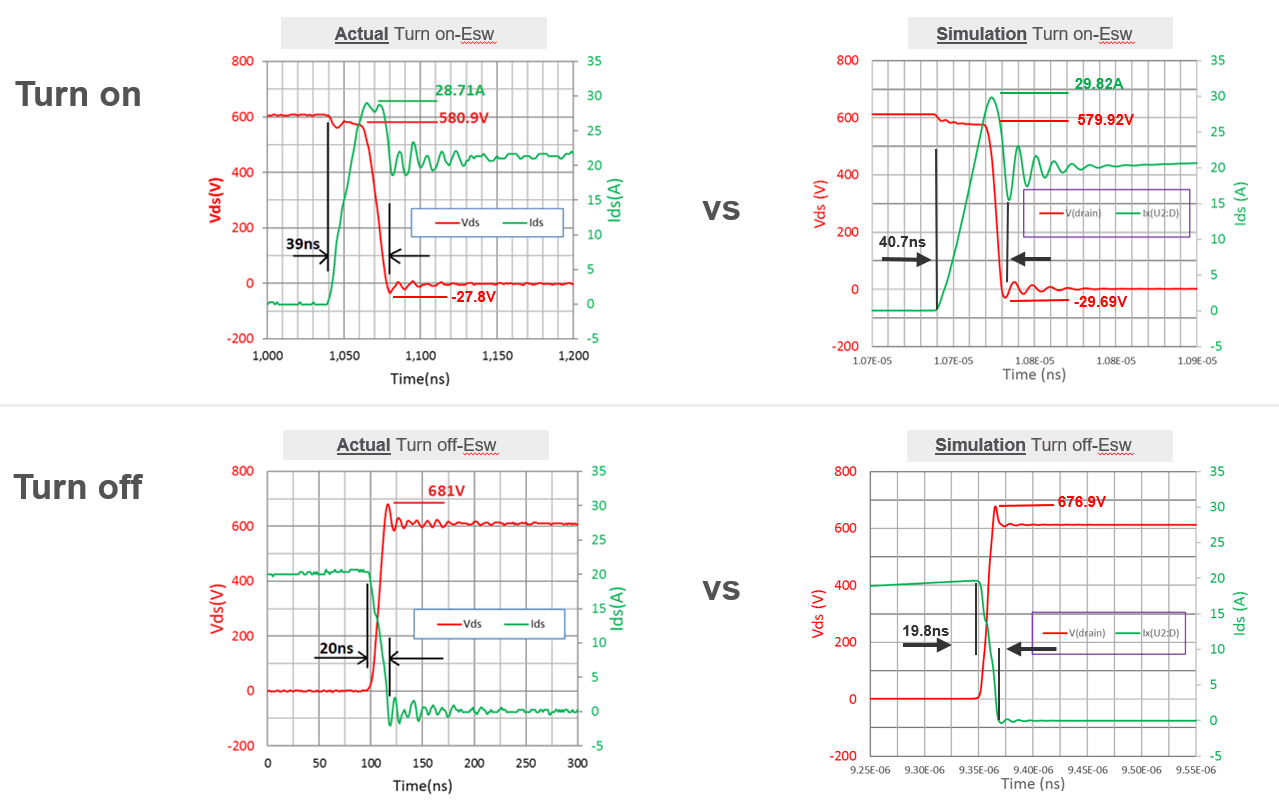

In our example, this gives an Lpkg value of 2.503 nH. Despite variations, this value can be taken as a good estimate and a reliable rule of thumb. Simulating after taking the inductances into account makes the dynamic model accurate (Figure 4).

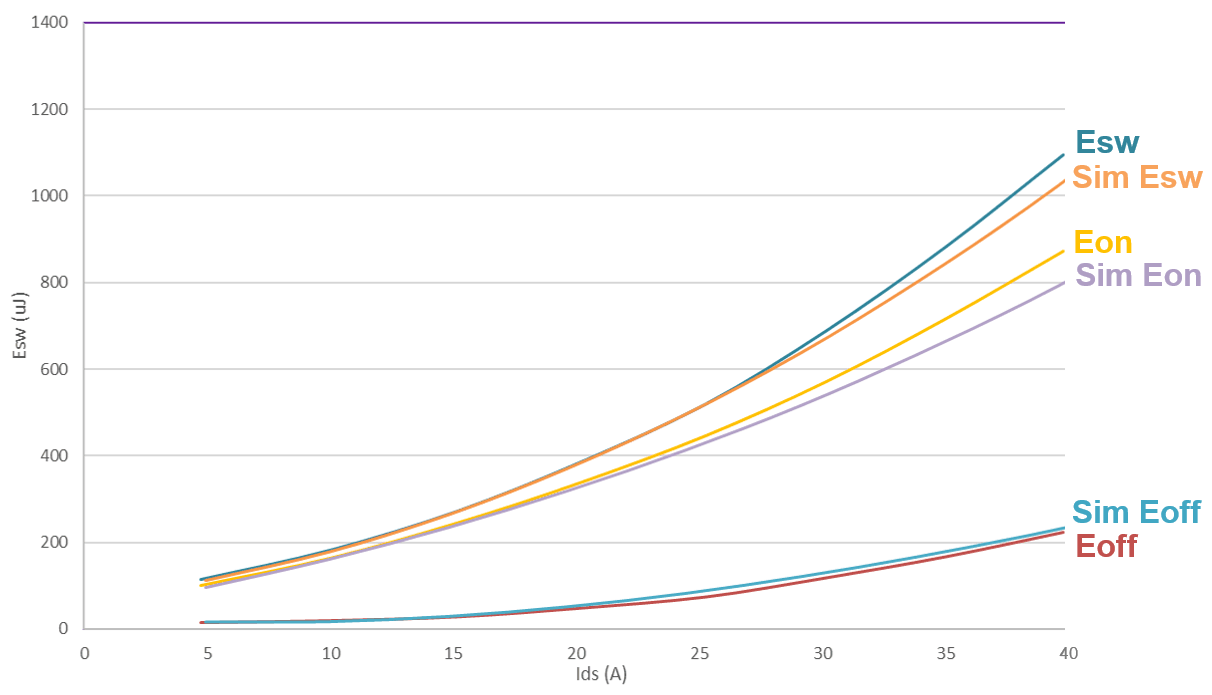

With the inductances factored in, total switching energy Esw as well as Eon and Eoff for actual and simulated double-pulse test become very close (Figure 5).

Using these rules of thumb for Lm and Lpkg, engineers can get fairly accurate loss and thermal calculations for their thermal budget.

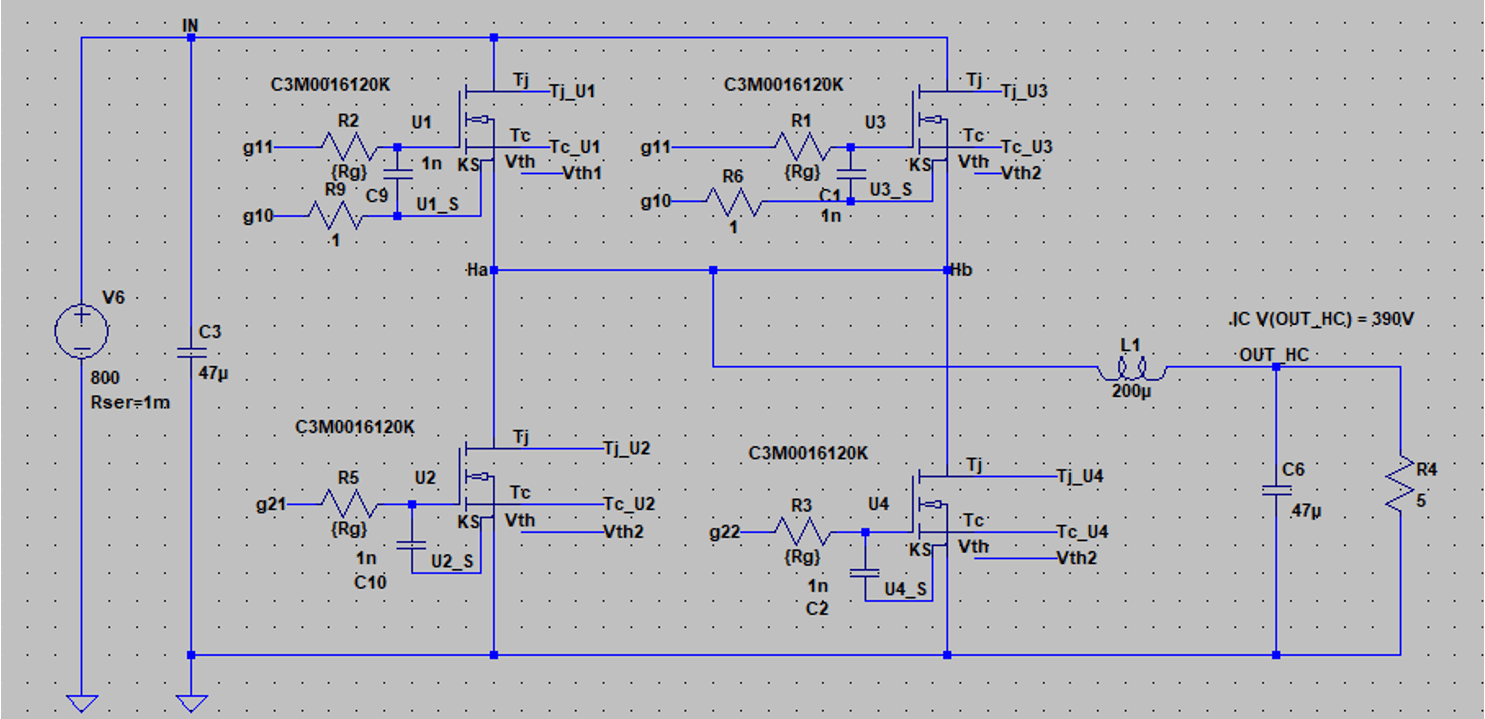

Paralleled MOSFETs

SiC MOSFETs are often placed in parallel to increase the current-carrying capability as well as power levels. There are some considerations to bear in mind, however:

- Current imbalance due to threshold voltage, VTH, differences

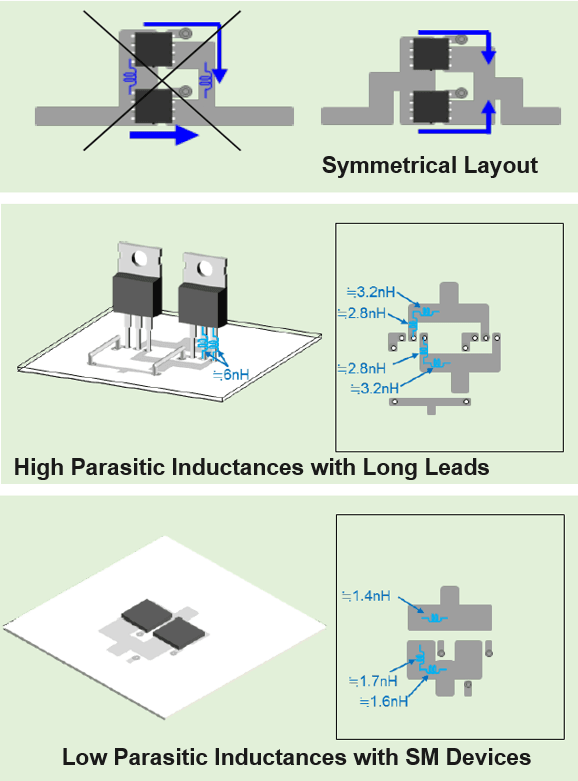

- Current imbalance due to asymmetrical parasitic inductances

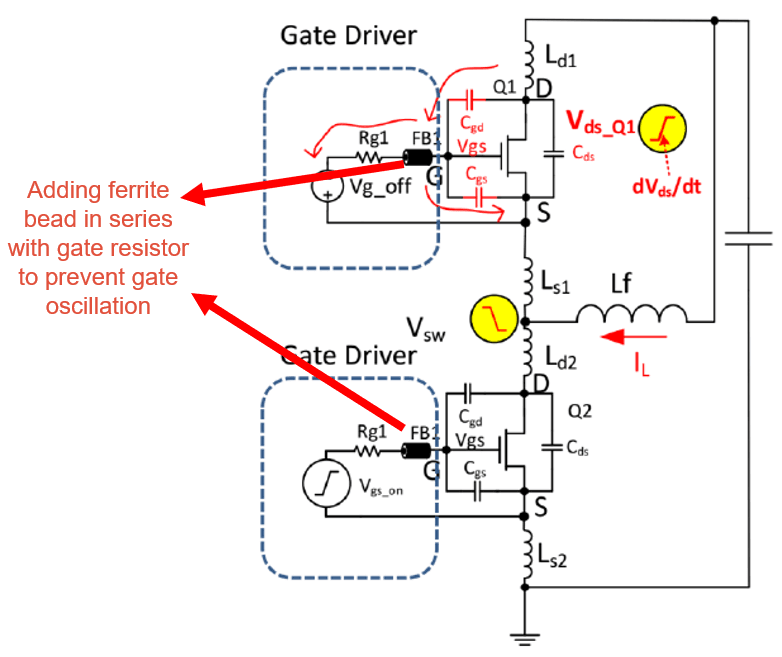

- Gate drive oscillation

With Wolfspeed SiC MOSFETs, there is little chance of mismatching device characteristics. However, engineers may be required to use other SiC parts with a wider tolerance of specification and may choose, say, a device with 2 V VTH and another with 3 V. The device with the lower threshold has a higher transient and because of that, higher switching losses and higher conduction losses, thus higher total power losses (Figure 6).

Parameter | MOSFET U1 | MOSFET U3 |

|---|---|---|

VTH(V) | 2 | 3 |

iRMS(A) | 29.821 | 25.745 |

iDC(A) | 21.11 | 18.69 |

EON(μJ) | 1011.5 | 609.77 |

EOFF(μJ) | 986.29 | 405.58 |

ETOTAL(μJ) | 1997.79 | 1014.35 |

Total Loss (W) | 216.53 | 115.87 |

MOSFET with lower threshold voltage

- Higher currents during transient and static period

- Higher switching losses, higher conduction loss and total power loss

Although both devices have the same gate resistance, RG, and are operating at the same temperature and switching frequency, modeling without any considerations results in U1 having over 200 W total losses and U3 just over 100 W. Simulated waveforms show that U1 peaks to about 70 A overshoot before falling to steady state of 50 A, whereas U3 peaks to about 49 A and settles to 30 A steady state. There is therefore a considerable mismatch in current carrying capability between the two devices as well as slight differences in turn-on and turn-off times.

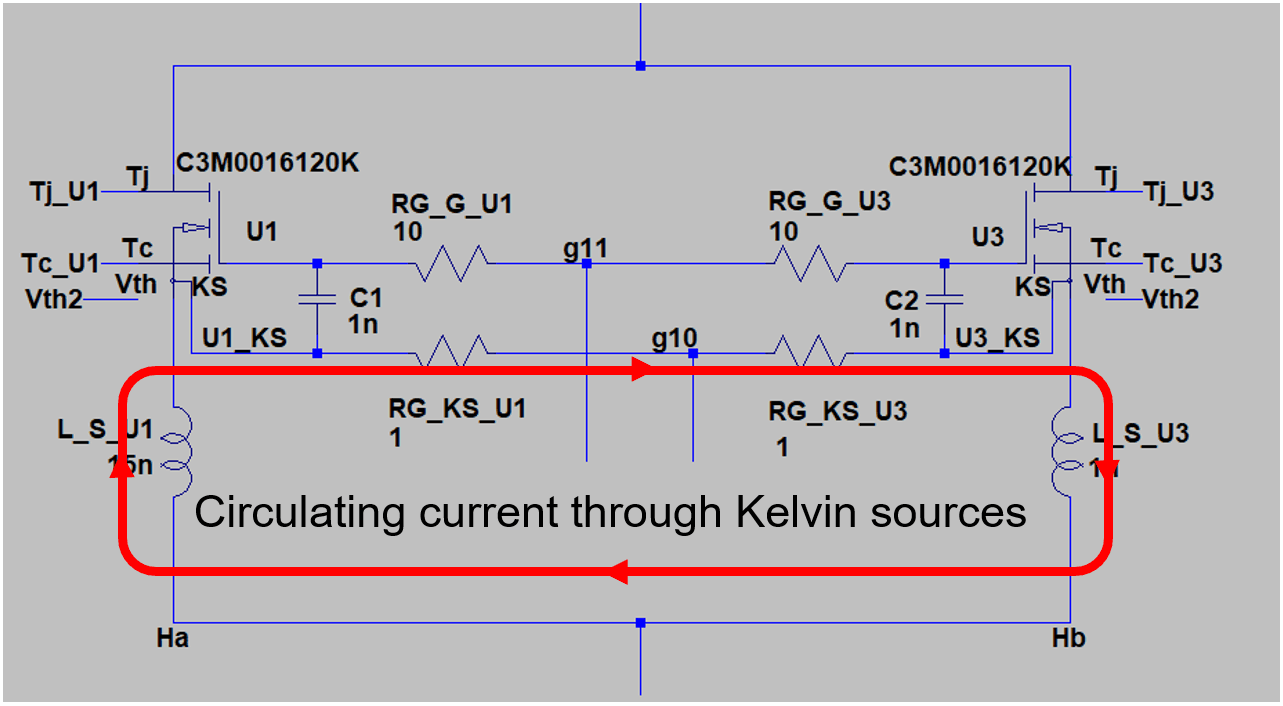

The second cause of current imbalance is asymmetric parasitics. Consider two devices, U1 and U3 (Figure 7) that have the same VTH but different source inductances. This causes considerably unbalanced di/dt’s, voltages across the stray inductances, gate drives, and drain currents. Simulated waveforms show that the current ramps up and down much faster for U3, and reaches higher values for IDC and IRMS, causing 17.9% higher switching loss and 18.3% higher total loss in that MOSFET.

Parameter | MOSFET U1 | MOSFET U3 |

|---|---|---|

VTH(V) | 3 | 3 |

Stray Ls(nH) | 15 | 1 |

iRMS(A) | 26.437 | 28.857 |

iDC(A) | 18.523 | 20.231 |

EON(μJ) | 391.85 | 1151.6 |

EOFF(μJ) | 974.05 | 459.02 |

ETOTAL(μJ) | 1365.9 | 1610.62 |

Total Loss (W) | 153.21 | 181.29 |

Mitigate mismatch with good design

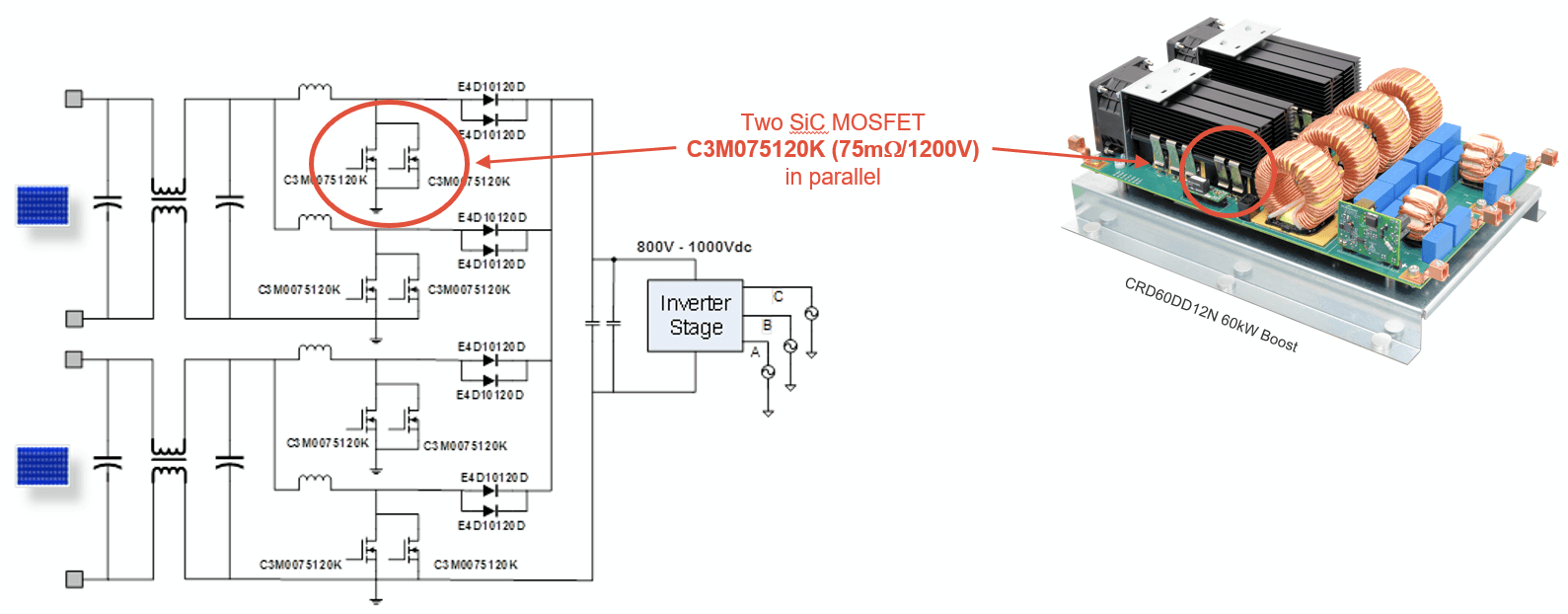

The impact of mismatched MOSFETs can be reduced considerably by incorporating good design practices. As an example, take the 60 kW solar inverter boost reference design CRD60DD12N that uses two 75 mΩ 1,200V C3M075120K MOSFETs in parallel (Figure 8). Using two of the TO-247 4-lead MOSFETs with the highest and lowest VTH from a sample of 60 parts still achieves hardware that works well, if good design practices are employed.

Parameter | Q1 | Q2 |

|---|---|---|

VTH(V) | 3.006 | 2.666 |

RDS_ON(mΩ) | 81.82 | 67.96 |

iRMS(A) | 3.64 | 4.01 |

Symmetrical PCB layout is critical for reducing circulating current in the gate loops of paralleled switches. Separate the power loop from the gate loop, provide enough damping to prevent gate oscillation, and add a ferrite bead at the gate leg to reduce voltage spikes and ringing on the gate that may cause part damage (Figure 9).

Due to these design practices, Q1 in the test circuit carries 47.6% of the total current, while Q2 carries 52.4%, reaching acceptable real-world results despite device mismatch.

Increasing tool choice

SiC-based designs can be modeled using Wolfspeed’s SpeedFit, LTSpice or PLECS. Whereas SpeedFit and LTSpice can be used freely by registering with Wolfspeed, PLECS comes with a subscription fee. The differences between the tools affects both the manner of generating simulations and their limitations, such as in handling parasitics and computation of losses.

To learn more about good design practices as well as tools to model your circuit, watch Designer’s Guide to Silicon Carbide Power — Modeling.